### 2015 Symposia on VLSI Technolog

#### 2015 Symposia on VLSI Technology and Circuits June 15th (Monday)

| Time        | Suzaku III          | Suzaku II          | Suzaku I                                          | Shunju III                                         | Shunju II                                  | Shunju I                                                                 |

|-------------|---------------------|--------------------|---------------------------------------------------|----------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------|

| 7:30-17:00  |                     |                    | Registration (Tech<br>*Press Release Timing: 7:30 | nology and Circuits)<br>0am JST, Monday, June 15th |                                            |                                                                          |

|             | 11:30-12:45 Short ( | Course Lunch Break |                                                   |                                                    |                                            |                                                                          |

| 8:30-17:00  |                     |                    |                                                   |                                                    | ology Short Course<br>d More Moore for IoT | 8:30-17:30<br><b>2015 Silicon Nanoelectronics</b><br>Workshop<br>(Day 2) |

| 17:00-17:30 |                     |                    |                                                   |                                                    |                                            |                                                                          |

| 19:00-22:10 |                     |                    | 19:00-22:10<br>2015 Spintronics Workshop on LSI   |                                                    |                                            |                                                                          |

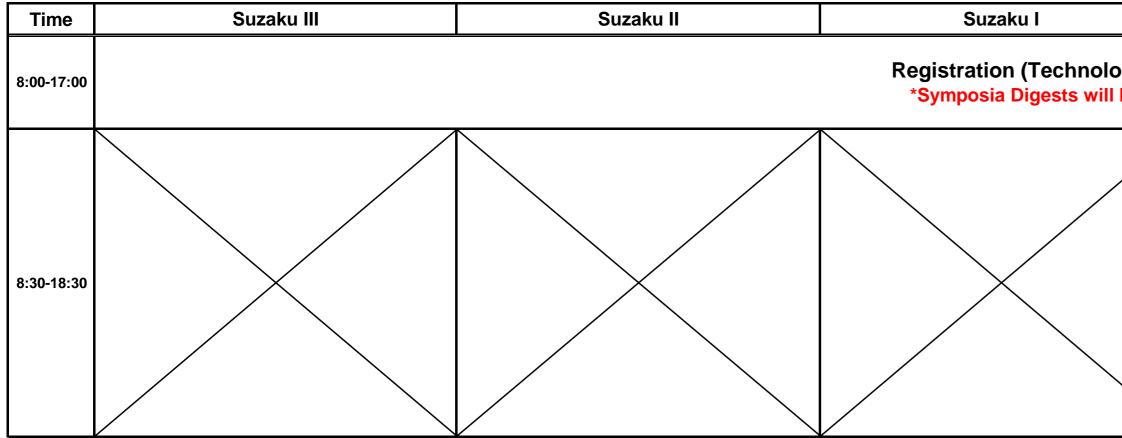

| ogy and Circuits | June 14th (Sunday) |

|------------------|--------------------|

|------------------|--------------------|

|     | Shunju III                                                      | Shunju II                                                          | Shunju I                                                          |

|-----|-----------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| ••• | d Silicon Nanoelectronics WS)<br>ributed from Monday, June 15th |                                                                    |                                                                   |

|     |                                                                 | 8:30-18:30<br>2015 Silicon Nanoelectronics<br>Workshop<br>(Poster) | 8:30-18:30<br>2015 Silicon Nanoelectronics<br>Workshop<br>(Day 1) |

## 2015 Symposia on VLSI Technology and Circuits June 16th (Tuesday)

| Time                       | Suzaku III                                                                                                         | Suzaku II                                 | Symposia on VLSI Tech<br>Suzaku I                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------|

| 7:30-17:00                 |                                                                                                                    |                                           | Registr                                                             |

| 8:20-10:05                 |                                                                                                                    |                                           |                                                                     |

| 10:30-12:10<br>12:20-13:30 |                                                                                                                    | 12:20-13:30 Short Course Lunch Break      |                                                                     |

| 13:30-15:35                | 10:30-17:10 Circuits Short Course 2<br>Analog and Digital Circuit Design for IoT<br>Swarms                         | 15:10-15:25 Short Course Coffee Break     | 10:30-17:10 Circuits Short Cours<br>VLSI Design for Big Data Manage |

| 15:50-17:30                |                                                                                                                    |                                           |                                                                     |

| 17:30-18:30                | IEEE Solid-States Circuits Society<br>Young Professionals and Grad Students Mentoring<br>and Career coaching event |                                           |                                                                     |

| 19:30-20:00                |                                                                                                                    |                                           |                                                                     |

|                            |                                                                                                                    | 20:00-22:00 Technology                    | Evening Panel Discussion                                            |

| 20:00-22:00                |                                                                                                                    |                                           | hat Will be Next?                                                   |

|                            | Technology Short Course:                                                                                           | June 15th (Monday) 8:30-17:00 / Shunju II |                                                                     |

Technology Short Course: June 15th (Monday) 8:30-17:00 / Shunju II, III 2015 Silicon Nanoelectronics Workshop: June 14th (Sunday) 8:30-18:30, 15th (Monday) 08:30-17:30 / Shunju I (for oral sessions), Shunju II (for posters) 2015 Spintronics Workshop on LSI: June 15th (Monday) 19:00-22:10 / Suzaku I

|          |                                                                                                                                     | Shunju III                                                                              | Shunju II                                                                               |                                | Shunju I                                                                                                                                         |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| stration | (Techno                                                                                                                             | logy and Circuits)                                                                      |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T1-1                                                                                                                                | 8:20-8:45                                                                               | T1 "Welcome and Plenary Session                                                         | า"                             |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     | Welcome and Opening Remarks                                                             |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T1-2                                                                                                                                | 8:45-9:25 (Plenary)                                                                     |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | AIST                                                                                                                                | Robotics for Innovation                                                                 |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T1-3                                                                                                                                | 9:25-10:05 ( <b>Plenary</b> )                                                           |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | Google System Challenges and Hardware Requirements for Future Consumer Devices: From Wearable to ChromeBooks and Devices in-between |                                                                                         |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T2-1                                                                                                                                | 10:30-10:55                                                                             | T2: Highlight                                                                           |                                |                                                                                                                                                  |  |  |  |  |  |

|          | 12-1                                                                                                                                |                                                                                         | g 2nd Generation Tri-Gate Transistors, 70 nm Gate Pitch                                 | 52 nm Metal                    | Pitch and 0 0/00 um2 SRAM Cells. Ontimi                                                                                                          |  |  |  |  |  |

|          | Intel                                                                                                                               | Power, High Performance and High Density                                                | · •                                                                                     |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T2-2                                                                                                                                | 10:55-11:20                                                                             |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | Panasonic                                                                                                                           | Highly Reliable TaOx ReRAM with Centraliz                                               | ed Filament for 28-nm Embedded Application                                              |                                |                                                                                                                                                  |  |  |  |  |  |

|          | T2-3                                                                                                                                | 11:20-11:45                                                                             |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | IBM                                                                                                                                 | High-Mobility High-Ge-Content Si1-xGex-Ol ~10nm Fin Width                               | PMOS FinFETs with Fins Formed Using 3D Germanium                                        | Condensatior                   | n with Ge Fraction Up to x~ 0.7, Scaled EOT                                                                                                      |  |  |  |  |  |

|          | T2-4                                                                                                                                | 11:45-12:10                                                                             |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          | The Univ. of<br>Tokyo                                                                                                               | Design and Demonstration of Reliability-Aw                                              | are Ge Gate Stacks with 0.5 nm EOT                                                      |                                |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     | T3: (FS) 7nm Node Logic                                                                 | : Technology and Beyond                                                                 |                                | T4: Reliability                                                                                                                                  |  |  |  |  |  |

|          | T3-1                                                                                                                                | 13:30-13:55 ( <b>Invited</b> )                                                          |                                                                                         | T4-1                           | 13:30-13:55                                                                                                                                      |  |  |  |  |  |

|          | The Univ.<br>of Tokyo                                                                                                               | III-V and Ge/strained SOI Tunneling FET Te                                              | echnologies for Low Power LSIs                                                          | Liverpool John<br>Moores Univ. | AC NBTI of Ge pMOSFETs: Impact of Ener<br>Defects on Lifetime Prediction                                                                         |  |  |  |  |  |

|          | T3-2                                                                                                                                | 13:55-14:20                                                                             |                                                                                         | T4-2                           | 13:55-14:20                                                                                                                                      |  |  |  |  |  |

| urse 1   | Intel                                                                                                                               | Variation-Tolerant Dense TFET Memory wit                                                | h Low VMIN Matching Low-Voltage TFET Logic                                              | Liverpool John<br>Moores Univ. | A Test-Proven As-Grown-Generation (A-G)<br>Predicting NBTI under Use-Bias                                                                        |  |  |  |  |  |

| igement  | T3-3                                                                                                                                | 14:20-14:45 ( <b>Invited</b> )                                                          |                                                                                         | T4-3                           | 14:20-14:45                                                                                                                                      |  |  |  |  |  |

|          | imec                                                                                                                                | Vertical Device Architecture for 5nm and Be                                             | eyond: Device & Circuit Implications                                                    | The Univ. of<br>Tokyo          | Impact of Random Telegraph Noise on Write St<br>Thin-BOX (SOTB) SRAM Cells at Low Supply V<br>Regime                                             |  |  |  |  |  |

|          | Т3-4                                                                                                                                | 14:45-15:10                                                                             |                                                                                         | T4-4                           | 14:45-15:10                                                                                                                                      |  |  |  |  |  |

|          | Massachusett<br>s Institute of<br>Technology                                                                                        | 15-nm Channel Length MoS2 FETs with Sir                                                 | ngle- and Double-Gate Structures                                                        | Toshiba                        | Further Investigations on Traps Stabilities in Random<br>Noise and the Application to a Novel Concept Physica<br>(PUF) with Robust Reliabilities |  |  |  |  |  |

|          | T3-5                                                                                                                                | 15:10-15:35                                                                             |                                                                                         | T4-5                           | 15:10-15:35                                                                                                                                      |  |  |  |  |  |

|          | imec                                                                                                                                |                                                                                         | Extension by Room Temperature and Hot Ion<br>7 (7nm) Technology Relevant Fin Dimensions | Univ. of<br>Minnesota          | High Frequency AC Electromigration Lifetin<br>Measurements from a 32nm Test Chip                                                                 |  |  |  |  |  |

|          | T5-1                                                                                                                                | T5: (FS) 3D Syste<br>15:50-16:15 (Invited)                                              | ms and Packaging                                                                        | T6: Ac<br>T6-1                 | Ivanced CMOS Technology: Ge FinFET / Com<br>15:30-16:15                                                                                          |  |  |  |  |  |

|          | TSMC                                                                                                                                |                                                                                         | egrated Fan-Out Wafer-Level-Packaging for Mobile                                        | imec                           | Strained Germanium Quantum Well p-FinFETs Fabric<br>Pitch Using Replacement Channel, Replacement Meta<br>Germanide-Free Local Interconnect       |  |  |  |  |  |

|          | T5-2                                                                                                                                | 16:15-16:40 ( <b>Invited</b> )                                                          |                                                                                         | T6-2                           | 16:15-16:40                                                                                                                                      |  |  |  |  |  |

|          | CEA-LETI                                                                                                                            | 3DVLSI with CoolCube Process: An Alterna                                                | tive Path to Scaling                                                                    | Purdue Univ.                   | First Experimental Demonstration of Ge 3D Circuits                                                                                               |  |  |  |  |  |

|          | T5-3                                                                                                                                | 16:40-17:05                                                                             |                                                                                         | T6-3                           | 16:40-17:05                                                                                                                                      |  |  |  |  |  |

|          | CEA-LETI                                                                                                                            | High Performance Low Temperature Activa<br>Integration of FD, TriGate, FinFET on Insula | ted Devices and Optimization Guidelines for 3D VLSI ator                                | imec                           | Characterization of Self-Heating in High-Mo<br>pMOS Devices                                                                                      |  |  |  |  |  |

|          | T5-4                                                                                                                                | 17:05-17:30                                                                             |                                                                                         | T6-4                           | 17:05-17:30                                                                                                                                      |  |  |  |  |  |

|          | EPFL                                                                                                                                | Ultra Fine-Pitch TSV Technology for Ultra-D                                             | Dense High-Q RF Inductors                                                               | Univ. of<br>California         | New Industry Standard FinFET Compact M<br>Technology Nodes                                                                                       |  |  |  |  |  |

| _        |                                                                                                                                     |                                                                                         |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     |                                                                                         | -20:00                                                                                  | 1                              |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     |                                                                                         | VLSI Technology<br>ary Celebration                                                      |                                |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     |                                                                                         | ening Panel Discussion                                                                  | 1                              |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     | Semiconductor Industry in 2                                                             | 020: Evolution or Revolution?                                                           |                                |                                                                                                                                                  |  |  |  |  |  |

|          |                                                                                                                                     |                                                                                         |                                                                                         |                                |                                                                                                                                                  |  |  |  |  |  |

| zed for Low                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

| ~8.5Å and                                                                                                                              |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

|                                                                                                                                        |

| gy Alternating                                                                                                                         |

|                                                                                                                                        |

|                                                                                                                                        |

| Model for                                                                                                                              |

|                                                                                                                                        |

|                                                                                                                                        |

| ability in Silicon-on-                                                                                                                 |

| ability in Onicon on                                                                                                                   |

| oltage in Sub-0.4V                                                                                                                     |

| oltage in Sub-0.4V                                                                                                                     |

| oltage in Sub-0.4V                                                                                                                     |

| Telegraph Signal                                                                                                                       |

| oltage in Sub-0.4V                                                                                                                     |

| oltage in Sub-0.4V                                                                                                                     |

| oltage in Sub-0.4V                                                                                                                     |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function                                                                        |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function                                                                        |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model                                                    |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin                               |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model                                                    |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin                               |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and                |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin                               |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and                |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and<br>FinFET CMOS |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and                |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and<br>FinFET CMOS |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and<br>FinFET CMOS |

| oltage in Sub-0.4V<br>Telegraph Signal<br>I Unclonable Function<br>ne<br>pact Model<br>cated on 45nm Fin<br>al Gate and<br>FinFET CMOS |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

| oltage in Sub-0.4V Telegraph Signal I Unclonable Function ne pact Model cated on 45nm Fin al Gate and FinFET CMOS obility Ge FinFET    |

# 2015 Symposia on VLSI Technology and Circuits June 17th (Wednesday)

| Time                     | Suzaku III                                                                                                            | Suzaku II                                                                                                                                                                        | Suzaku I         |                       | Shunju III Shunju II                                                                                                                                | Shunju I                                                                                                         | I                  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|

| 7:30-17:00               |                                                                                                                       |                                                                                                                                                                                  | Registration (Te | echnol                | ogy and Circuits)                                                                                                                                   | -                                                                                                                |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  |                  |                       | C1 "Welcome and Plenary Session                                                                                                                     | n"                                                                                                               |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  |                  | :1-1                  | 8:30-8:45                                                                                                                                           |                                                                                                                  |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  |                  |                       | Welcome and Opening Remarks                                                                                                                         |                                                                                                                  |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  | C1               | 1-2                   | 8:45-9:25 (Plenary)                                                                                                                                 |                                                                                                                  |                    |

| 8:30-10:05               |                                                                                                                       |                                                                                                                                                                                  | Hit              | itachi                | Profiting from IoT: The Key is Very-Large-Scale Happiness Integration                                                                               |                                                                                                                  |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  | C1               | 1-3                   | 9:25-10:05 (Plenary)                                                                                                                                |                                                                                                                  |                    |

|                          |                                                                                                                       |                                                                                                                                                                                  | Bo               | obert<br>osch<br>mbH  | Automated Driving – Impacts on the Vehicle Architecture                                                                                             |                                                                                                                  |                    |

| (                        | C3: SARADCs & SC Filter<br>C3-1 10:30-10:55                                                                           | C2: Image Processing<br>C2-1 10:30-10:55                                                                                                                                         |                  | FS1-1                 | JFS1: Ultra Low Power for IoT<br>10:30-10:55 (Invited)                                                                                              | T7: Memory Technolo<br>T7-1 10:30-10:55                                                                          | ogy: PC RAM        |

| ι                        | Iniv of A Sharp Programmable Passive Filter                                                                           | A 0.5-Degree Error 10mW CMOS Image<br>KAIST Sensor-Based Gaze Estimation Processor with<br>Logarithmic Processing                                                                | Re               | 000000                | Automotive Low Power Technology for IoT Society                                                                                                     | Hitachi 2.8-GB/s-Write and 670-MB/s<br>Vertical Chain-Cell-Type Pha                                              |                    |

| C                        | C3-2 10:55-11:20                                                                                                      | C2-2 10:55-11:20                                                                                                                                                                 | JF               | FS1-2                 | 10:55-11:20 (Invited)                                                                                                                               | T7-2 10:55-11:20                                                                                                 |                    |

|                          | Signal-Dependent Charge Recycling for                                                                                 | Univ. of A 23mW Face Recognition Accelerator in<br>Michigan 40nm CMOS with Mostly-Read 5T Memory                                                                                 | im               | nec                   | IoT: the Impact of Things                                                                                                                           | MacronixGreater than 2-bits/Cell MLCInternationalPhase Change Memory Usin                                        |                    |

| C                        | C3-3 11:20-11:45                                                                                                      | C2-3 11:20-11:45                                                                                                                                                                 | JF               | FS1-3                 | 11:20-11:45                                                                                                                                         | T7-3 11:20-11:45                                                                                                 |                    |

| 10:30-12:35<br>          |                                                                                                                       | Univ. of<br>Michigan A 640M pixel/s 3.65mW Sparse Event-Driven<br>Neuromorphic Object Recognition Processor<br>with On-Chip Learning                                             |                  | ualcomm<br>echnologie | Transistor-Interconnect Mobile System-On-Chip Co-Design Method for Holistic Battery Energy<br>Minimization                                          | LEAP A 50-nm 1.2-V GexTe1-x/Sb2<br>Switching Random-Access M                                                     |                    |

| C                        | C3-4 11:45-12:10                                                                                                      | C2-4 11:45-12:10                                                                                                                                                                 | JF               | FS1-4                 | 11:45-12:10                                                                                                                                         | T7-4 11:45-12:10                                                                                                 |                    |

| 1                        | Rokyo A 9.35-ENOB, 14.8 fJ/ConvStep Fully-<br>Passive Noise-Shaping SAR ADC                                           | A 33 nJ/Vector Descriptor Generation<br>KAIST Processor for Low-Power Object<br>Recognition                                                                                      | LE               |                       | Sub- $\mu$ W Standby Power, <18 $\mu$ W/DMIPS@25MHz MCU with Embedded Atom-Switch Programmable Logic and ROM                                        | Operation Fundamentals in 12M<br>CEA-LETI on Innovative Ge-Rich GST Mate<br>Performance                          |                    |

| (                        | C3-5 12:10-12:35                                                                                                      | C2-5 12:10-12:35<br>NTT Media                                                                                                                                                    | JF               | FS1-5                 | 12:10-12:35 (Invited)                                                                                                                               | T7-5 12:10-12:35                                                                                                 |                    |

|                          |                                                                                                                       | Intelligence Single-Chip 4K 60fps 4:2:2 HEVC Video<br>Laboratorie Encoder LSI with 8K Scalability<br>s                                                                           | ST<br>tro        | TMicroelec<br>onics   | Breakthrough Technologies and Reference Designs for New IoT Applications                                                                            | Macronix<br>International A Novel Self-Converging Wri<br>Phase Change Memory for S<br>Application                |                    |

|                          | C5: Low Power Wireless Transceivers<br>C5-1 13:55-14:20                                                               | C4: Image Sensors<br>C4-1 13:55-14:20                                                                                                                                            |                  | FS2-1                 | JFS2: Emerging NVM<br>13:55-14:20 (Invited)                                                                                                         | T8: Process Technology: Co           T8-1         13:55-14:20                                                    | ontact / Intere    |

|                          | A 3.5mW 315/400MHz                                                                                                    | Hokkaido Image Sensor/Digital Logic 3D Stacked Module                                                                                                                            |                  |                       | The Progresses of MRAM as a Memory to Save Energy Consumption and Its Potential for Further                                                         | STMicroelectr Considerations for Efficient Contact                                                               |                    |

|                          | Tunable Radio SoC with Integrated Digital<br>Baseband and MAC Processor in 40nm CMOS                                  | Univ. Featuring Inductive Coupling Channels for High<br>Speed/Low-Noise Image Transfer                                                                                           |                  | oshiba                | Reduction                                                                                                                                           | onics Depinning - Impact of MIS Contacts<br>Characteristics                                                      | s on 10nm Node n   |

|                          |                                                                                                                       | C4-2 14:20-14:45<br>A 0.66e-rms Temporal-Readout-Noise 3D-                                                                                                                       | JF               | FS2-2                 | 14:20-14:45 (Invited)                                                                                                                               | T8-2 14:20-14:45                                                                                                 |                    |

| C                        | Jniv. ofA 1Gb/s Energy Efficient Triple-ChannelCaliforniaUWB-Based Cognitive Radio                                    | TSMC Stacked CMOS Image Sensor with Conditional<br>Correlated Multiple Sampling (CCMS) Technique                                                                                 | Те               | echnology             | Challenges for High-Density 16Gb ReRAM with 27nm Technology                                                                                         | Applied Ultra-Low Contact Resistivity<br>Materials Contact for nMOSFET                                           | y with Highly D    |

| (<br>13:55-16:00         |                                                                                                                       | C4-3 14:45-15:10                                                                                                                                                                 | JF               | FS2-3                 | 14:45-15:10                                                                                                                                         | Т8-3 14:45-15:10<br>ІВМ Т. Ј.                                                                                    |                    |

|                          | ARM A 0.6V All-Digital Body-Coupled Wakeup<br>Transceiver for IoT Applications                                        | National<br>Tsing Hua<br>Univ.<br>A 0.4V Self-Powered CMOS Imager with 140dB<br>Dynamic Range and Energy Harvesting                                                              |                  | enesas<br>lectronics  | Low-Power Embedded ReRAM Technology for IoT Applications                                                                                            | Watson<br>Research<br>Center                                                                                     | onnects Beyon      |

| C                        | C5-4 15:10-15:35                                                                                                      | C4-4 15:10-15:35                                                                                                                                                                 | JF               | FS2-4                 | 15:10-15:35                                                                                                                                         | T8-4 15:10-15:35                                                                                                 |                    |

|                          | STMicroeleA Self-Powered IPv6 Bidirectional WirelessctronicsSensor & Actuator Network for Indoor Conditions           | Tohoku<br>Univ.A Linear Response Single Exposure CMOS<br>Image Sensor with 0.5e- Readout Noise and<br>76ke- Full Well Capacity                                                   |                  |                       | RRAM-Based 7T1R Nonvolatile SRAM with 2x Reduction in Store Energy and 94x Reduction in Restore Energy for Frequent-Off Instant-On Applications     | Stanford Univ. Cu Diffusion Barrier: Grapher<br>Ultimate Interconnect Scaling                                    | ene Benchmar<br>າg |

|                          |                                                                                                                       | C4-5 15:35-16:00                                                                                                                                                                 | JF               | FS2-5                 | 15:35-16:00                                                                                                                                         | T8-5 15:35-16:00                                                                                                 |                    |

| 1                        | NationalA 794Mbps 135mW Iterative Detection andTsing HuaDecoding Receiver for 4x4 LDPC-Coded MIMOJniv.Systems in 40nm | A 3D Stacked CMOS Image Sensor with<br>Olympus 16Mpixel Global-Shutter Mode and 2Mpixel<br>10000fps Mode Using 4 Million Interconnections                                        | Ch               | huo Univ.             | Reliability Enhancement of 1Xnm TLC for Cold Flash and Millennium Memories                                                                          | KAIST Improved Electromigration-R<br>by Graphene-Based Capping                                                   |                    |

| (                        | <b>C7: Optical Links</b><br>C7-1 16:15-16:40                                                                          | C6: Bio Monitoring Circuits<br>C6-1 16:15-16:40                                                                                                                                  | Tg               | Q_1                   | T9: Memory Technology: ReRAM<br>16:15-16:40                                                                                                         | T10: Advanced CMOS Technology: Na           T10-1         16:15-16:40                                            | Nanowire FET       |

| ι                        | Jniv. of A 19.6-Gbps CMOS Optical Receiver with                                                                       | Univ. of<br>California<br>A 16-Channel Wireless Neural Interfacing SoC<br>with RF-Powered Energy-Replenishing Adiabatic                                                          |                  |                       | Self-Limited RRAM with ON/OFF Resistance Ratio Amplification                                                                                        | Gate-All-Around NWFETs vs. Tr<br>imec vs. Extensionless and Conventio                                            | tional Junction D  |

|                          |                                                                                                                       | C6-2 16:40-17:05                                                                                                                                                                 | То               | 9-2                   | 16:40-17:05                                                                                                                                         | Controlled EWF Modulation for I<br>T10-2 16:40-17:05                                                             | Multi-VT CMOS      |

|                          | lational                                                                                                              | Enabling Closed-Loop Neural Interface: A Bi-<br>Univ. of Directional Interface Circuit with Stimulation                                                                          |                  |                       | Novel Selector for High Density Non-Volatile Memory with Ultra-Low Holding Voltage and 10^7                                                         | IBM T. J.                                                                                                        | tod with Minim     |

| 16:10-17:55 <sup> </sup> | aiwan Transcoivers in 40nm CMOS                                                                                       | Michigan Artifact Cancellation and Cross-Channel CM<br>Noise Suppression                                                                                                         | A*               |                       | On/Off Ratio                                                                                                                                        | Watson Si Nanowire CMOS Fabricate<br>Research RMG FinFET Technology Sh<br>Center                                 |                    |

|                          | 27-3 17:05-17:30                                                                                                      | C6-3 17:05-17:30                                                                                                                                                                 | ТЭ               | 9-3                   | 17:05-17:30                                                                                                                                         | T10-3 17:05-17:30                                                                                                |                    |

| C                        |                                                                                                                       | Case<br>Western<br>Reserve<br>Univ.<br>Neurochemical Thermostat: A Neural Interface<br>SoC with Integrated Chemometrics for Closed-<br>Loop Regulation of Brain Dopamine         | im               | 100                   | a-VMCO: A Novel Forming-Free, Self-Rectifying, Analog Memory Cell with Low-Current Operation,<br>Nonfilamentary Switching and Excellent Variability | Si-cap-free SiGe p-Channel FinFET<br>imec Replacement Metal Gate Process: In<br>Performance Improvement by High- | Interface Trap De  |

| C                        |                                                                                                                       | C6-4 17:30-17:55                                                                                                                                                                 | ТЭ               | 9-4                   | 17:30-17:55                                                                                                                                         | T10-4 17:30-17:55                                                                                                |                    |

|                          |                                                                                                                       | Univ. of<br>MichiganToward 1024-Channel Parallel Neural Recording:<br>Modular $\Delta$ - $\Delta\Sigma$ Analog Front-End Architecture with<br>4.84fJ/C-s•mm2 Energy-Area Product | im               | 200                   | A Novel CBRAM Integration Using Subtractive Dry-Etching Process of Cu Enabling High-<br>Performance Memory Scaling Down to 10nm Node                | Massachusett<br>s Institute of<br>Technology HoS2 FET Fabrication and M<br>Flexible Electronics                  | Modeling for L     |

|                          |                                                                                                                       |                                                                                                                                                                                  | ·                |                       | 19:00-21:00                                                                                                                                         |                                                                                                                  |                    |

| 19:00-21:00              |                                                                                                                       |                                                                                                                                                                                  |                  |                       | Joint Banquet                                                                                                                                       |                                                                                                                  |                    |

| itions of a 3D<br>emory Array                           |

|---------------------------------------------------------|

| tra High Density<br>sing Scheme                         |

|                                                         |

| ice Topological-<br>)                                   |

| e Memory Based<br>High Reliability                      |

|                                                         |

| 2-bits/Cell<br>/lemory (SCM)                            |

| onnect                                                  |

|                                                         |

| tion via Fermi Level<br>MOSFET DC                       |

| oped Si:P                                               |

| The 7 nm Node                                           |

| ed to TaN for                                           |

| u Interconnects                                         |

| 2D Materials                                            |

| Ts: Junctionless<br>vices with                          |

| I Deviation from<br>Performance                         |

| ound Transistors in a<br>sity Reduction and<br>m Anneal |

| rge-Scale                                               |

|                                                         |

### 2015 Symposia on VLSI Technology and Circuits June 18th (Thursday)

|                  | 0                                                                                                                                                        |                                                                                                                                                                                | mposia on VLSI Technology and                                                                                                 | •                                                                                                                                           |                                                                                                       |                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time             | Suzaku III                                                                                                                                               | Suzaku II                                                                                                                                                                      | Suzaku I                                                                                                                      | Shunju III                                                                                                                                  | Shunju II                                                                                             | Shunju I                                                                                                                                                                                                   |

| 8:00-17:00       | On Disco and Dalay Looks I have                                                                                                                          | 00. (E0) Outleme for Dir Dete Monomout                                                                                                                                         | Registration (Technol                                                                                                         | ,                                                                                                                                           |                                                                                                       |                                                                                                                                                                                                            |

|                  | C9: Phase and Delay Locked Loops<br>C9-1 8:30-8:55                                                                                                       | C8: (FS) Systems for Big Data Management<br>C8-1 8:30-8:55 (Invited)                                                                                                           |                                                                                                                               | T11: Advanced CMOS Technolo<br>T11-1 8:30-8:55                                                                                              | ogy: SI FINFET Device & Process                                                                       | T12: Memory Technology: MTJ and Related DevicesT12-18:30-8:55                                                                                                                                              |

| 1                | SeoulAn All-Digital Bang-Bang PLL Using Two-PointNationalModulation and Background Gain Calibration forUniv.Spread Spectrum Clock Generation             | Processing                                                                                                                                                                     |                                                                                                                               | imec RMG nMOS 1st Process Enabling 10x Lower                                                                                                | er Gate Resistivity in N7 Bulk FinFETs                                                                | Tohoku<br>Univ.Novel Oxygen Showering Process (OSP) for Extreme<br>Damage Suppression of Sub-20nm High Density p-<br>MTJ Array without IBE TreatmentT40.00.55.0.00                                         |

|                  | C9-28:55-9:20NationalA Digital Bang-Bang Phase-Locked Loop with<br>Automatic Loop Gain Control and Loop Latency<br>Univ.Univ.Reduction                   | C8-2 8:55-9:20<br>Inductively-Powered Wireless Solid-State Drive<br>(SSD) System with Merged Error Correction of<br>High-Speed Non-Contact Data Links and NAND<br>Flash Memory |                                                                                                                               | T11-2 8:55-9:20<br>High Sigma Measurement of Random Thresh<br>Technology                                                                    | hold Voltage Variation in 14nm Logic FinFET                                                           | T12-28:55-9:20Tohoku<br>Univ.10 nmφ Perpendicular-Anisotropy CoFeB-MgO<br>Magnetic Tunnel Junction with Over 400°C High<br>Thermal Tolerance by Boron Diffusion Control                                    |

|                  | C9-3 9:20-9:45<br>Univ. of<br>Minnesota A 0.4-1.6GHz Spur-Free Bang-Bang Digital PLL<br>in 65nm with a D-Flip-Flop Based Frequency<br>Subtractor Circuit | C8-3 9:20-9:45<br>Privacy-Protection Solid-State Storage (PP-<br>Chuo Univ. SSS) System: Automatic Lifetime Management<br>of Internet-Data's Right to be Forgotten             |                                                                                                                               | T11-39:20-9:45TSMCHigh Voltage I/O FinFET Device Optimization                                                                               | n for 16nm System-on-a-Chip (SoC) Technology                                                          | T12-39:20-9:45Univ. of<br>MinnesotaAn 8-bit Analog-to-Digital Converter Based on<br>the Voltage-Dependent Switching Probability of<br>a Magnetic Tunnel Junction                                           |

|                  | C9-4 9:45-10:10<br>A 450-fs Jitter PVT-Robust Fractional-<br>Resolution Injection-Locked Clock Multiplier                                                | C8-4 9:45-10:10 (Invited)<br>Caching Mechanisms towards Single-Level                                                                                                           |                                                                                                                               | T11-4 9:45-10:10                                                                                                                            |                                                                                                       | T12-4 9:45-10:10<br>Demonstration of an MgO Based Anti-Fuse<br>TDK-Headway OTP Design Integrated With a Fully Functional                                                                                   |

|                  | Using a DLL-Based Calibrator with Replica-<br>Delay-Cells                                                                                                | Storage Systems for Internet of Things                                                                                                                                         |                                                                                                                               | Research                                                                                                                                    | •                                                                                                     | STT-MRAM at the Mbit Level                                                                                                                                                                                 |

|                  | C11: Nyquist ADC and DAC<br>C11-1 10:30-10:55                                                                                                            | C10 (FS): IoT and Smart Systems<br>C10-1 10:30-10:55 (Invited)                                                                                                                 |                                                                                                                               | T13: Advanced CMOS Technolog<br>T13-1 10:30-10:55                                                                                           | gy: X-On Insulator (X-OI) Devices                                                                     | T14: Memory Technology: 3D NAND Flash & Other NVMT14-110:30-10:55                                                                                                                                          |

|                  | Texas A&MA 25GS/s 6b TI Binary Search ADC with<br>Univ.Univ.Soft-Decision Selection in 65nm CMOS                                                         | Hitachi Embedded Image Recognition Systems for<br>Advanced Safety Vehicles                                                                                                     |                                                                                                                               | STMicroelec<br>tronics                                                                                                                      | e for Ultra-Low Voltage Operation                                                                     | Macronix A Novel Dichotomic Programming Algorithm<br>International Applied to 3D NAND Flash                                                                                                                |

|                  | C11-2 10:55-11:20                                                                                                                                        | C10-2 10:55-11:20                                                                                                                                                              |                                                                                                                               | T13-2 10:55-11:20                                                                                                                           | Technology on Silicon-on-Thin-Buried-Oxide (SOTB) for                                                 | T14-210:55-11:20SeoulComprehensive Analysis of Retention Characteristics                                                                                                                                   |

|                  | Columbia A 3-10fJ/Conv-Step 0.0032mm2 Error-<br>Univ. Shaping Alias-Free Asynchronous ADC                                                                | Panasonic High-Level Video Analytics PC Subsystem Using<br>SoC with Heterogeneous Multi-Core Architecture                                                                      |                                                                                                                               | LEAP Ultra-Low Leakage Applications                                                                                                         | Technology on Silicon-on-Thin-Burled-Oxide (SOTB) for                                                 | Nationalin 3-D NAND Flash Memory Cells with Tube-TypeUniv.Poly-Si Channel Structure                                                                                                                        |